There are a couple of excellent articles on the effects of sample clock phase noise on DAC and ADC performance from Analog Devices.

Analyzing and Managing the Impact of Supply Noise and Clock Jitter on High Speed DAC Phase Noise

Sampled Systems and the Effects of Clock Phase Noise and Jitter.

Also another good paper from TI.

Why phase noise matters in RF sampling converters.

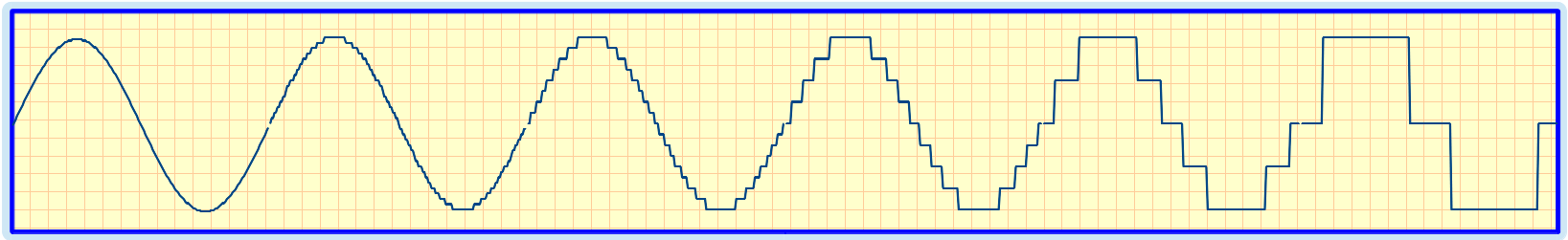

There is a trend in radio system design towards doing ever more of the signal processing in the digital domain. This has been enabled by DAC, ADC, and signal processing blocks, with ever faster sample rates, driven by the process shrinks as predicted by Moore’s Law. These process shrinks have also delivered lower power consumption making this design approach suitable for battery powered products and easing thermal design issues.

In all analogue radio designs, the phase noise of the local oscillator was key to radio performance. While this is still true of mixed analogue/digital designs, arguably the DAC/ADC clock has become just as important. When these clocks were in the 10s of MHz supplying a good quality clock was achieved by buying a good quality crystal oscillator. Now these clocks are in the 100s of MHz and GHz, achieving low phase noise and hence jitter is not so straight forward, as off-the-shelf crystal oscillators are only available up to about 100MHz. Beyond that oscillator modules use PLL based multipliers which inevitably add phase noise. At Golledge I have designed a 290MHz crystal oscillator using one of their high frequency fundamental mode resonators. Much above this, ultra low phase noise sources must look to other high Q resonators, such as SAW resonators. I hope to write more on this later.